Tugas Pendahuluan 1 (Modul 2)

1. Kondisi

[Kembali]

Percobaan 1, Kondisi 17

Buatlah rangkaian J-K flip flop dan D flip flop seperti pada gambar pada percobaan 1 dengan ketentuan input B0=1, B1=0, B2=don’t care, B3=don’t care, B4=don’t care, B5=don’t care, B6=don’t care led diganti logicprobe.

2. Alat dan Bahan [Kembali]

- IC 7474 (D Flip Flop)

- IC 74LS112 (JK Flip Flop)

- Logicprobe (BIG)

- Switch SPDT

- VCC

- Ground

3. Gambar Rangkaian Simulasi

[Kembali]

4. Video Simulasi

[Kembali]

5. Prinsip Kerja Rangkaian

[Kembali]

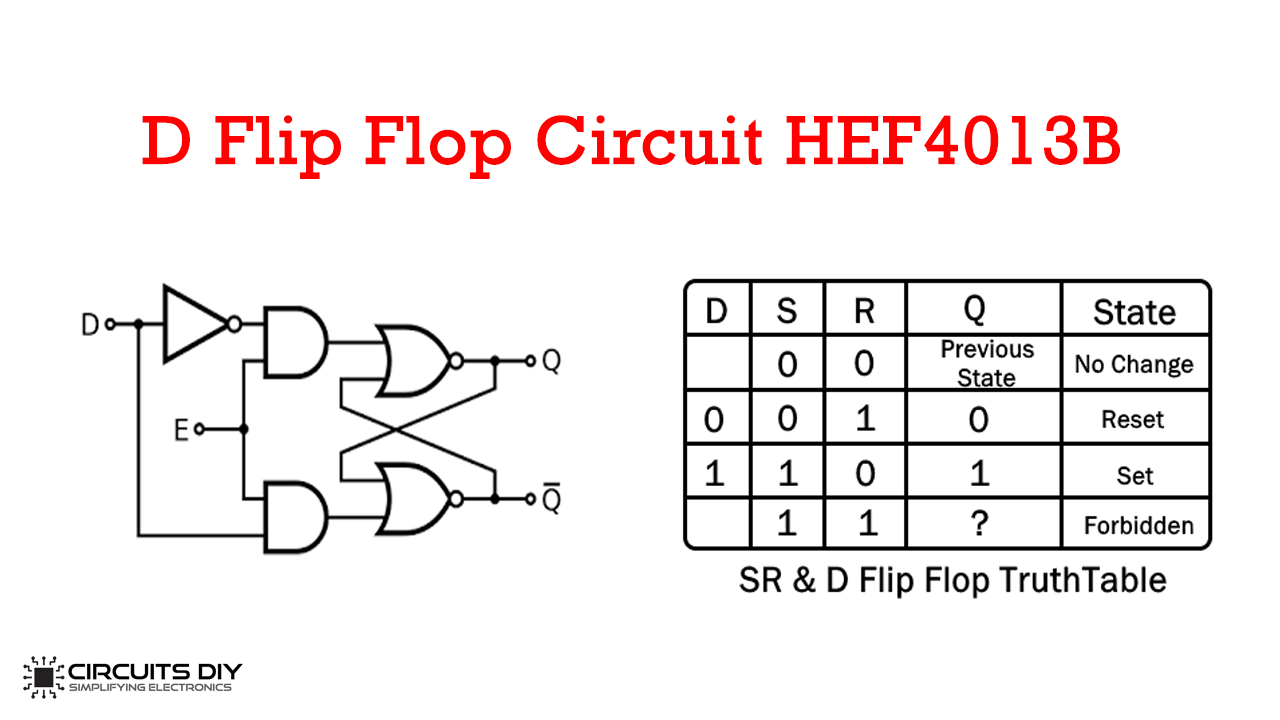

- D Flip-Flop

Apabila input clock berlogika 1 “High” maka input pada jalur data akan di teruskan ke rangkaian RS flip flop, dimana pada saat input jalur Data 1 “High” maka kondisi tersebut adalah Set Q menjadi 1 “High” dan pada saat jalur Data diberikan input 0 “Low” maka kondisi yang terjadi adala Reset Q menjadi 0 “Low”.

Kemudian Pada saat input Clock berlogika rendah maka data output pada jalur Q akan ditahan (memori 1 bit) walaupun logika pada jalur input Data berubah. Kondisi inilah yang disebut sebagai dasar dari memory 1 bit.

- J-K Flip-Flop

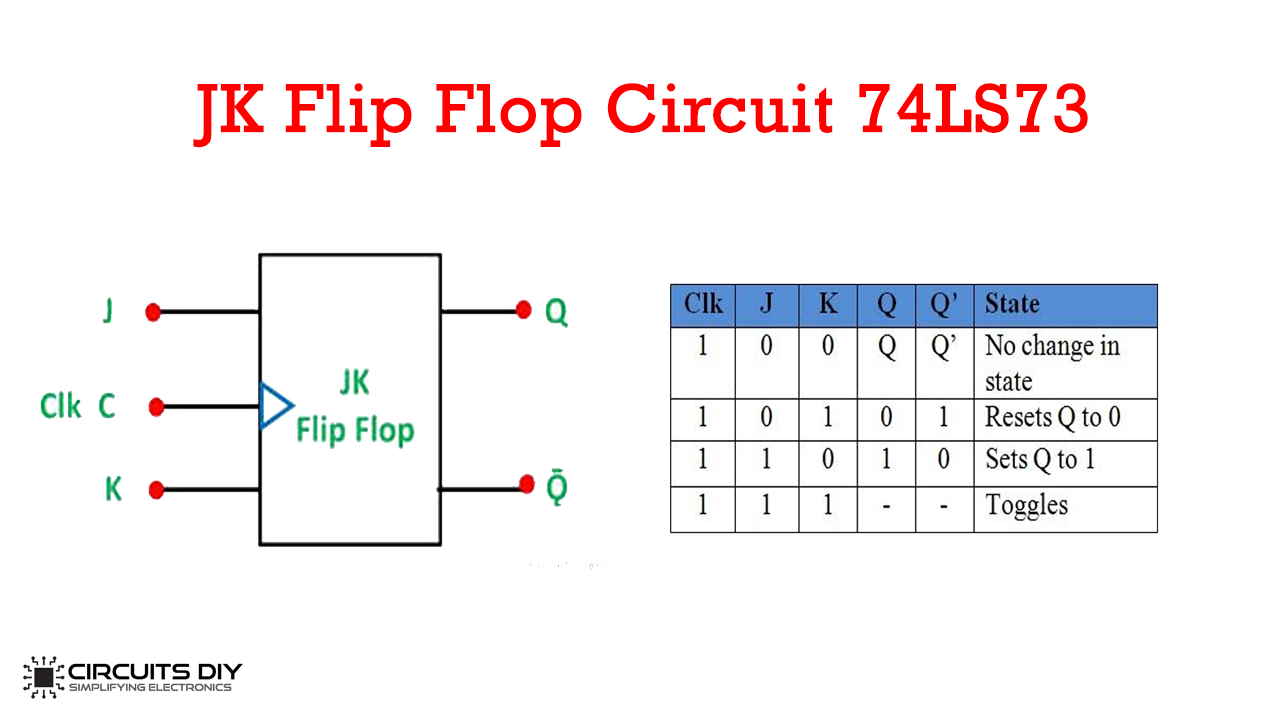

JK flip-flop adalah salah satu macam Flip Flop yang paling umum digunakan. Pada flip-flop ini terdapat 3 buah input yaitu J, K dan CLK, J dan K berfungsi sebagai pengendali.

Ketika J = 0 dan K = 0 maka output Q akan tetap seperti keadaan semula walaupun input CLK berubah-ubah.

Ketika J = 1 dan K = 0 , maka output Q akan di set (1) pada saat pulsa CLK input bergerak dari 1 ke 0.

Ketika J = 0 dan K = 1 maka output Q akan reset (0) pada saat pulsa CLK input bergerak dari 1 ke 0.

Tetapi jika J = 1 dan K = 1 maka JK flip-flop akan berfungsi sebagai T flip-flop yaitu output akan berubah Jika CLK bergerak dari 1 ke 0 . Kondisi ini disebut 'Toggle'.

- D Flip-Flop

Apabila input clock berlogika 1 “High” maka input pada jalur data akan di teruskan ke rangkaian RS flip flop, dimana pada saat input jalur Data 1 “High” maka kondisi tersebut adalah Set Q menjadi 1 “High” dan pada saat jalur Data diberikan input 0 “Low” maka kondisi yang terjadi adala Reset Q menjadi 0 “Low”.

Kemudian Pada saat input Clock berlogika rendah maka data output pada jalur Q akan ditahan (memori 1 bit) walaupun logika pada jalur input Data berubah. Kondisi inilah yang disebut sebagai dasar dari memory 1 bit.

- J-K Flip-Flop

6. Link Download

[Kembali]